# **Personal Computer**

# Service Reference Manual

# **MultiSpeed**

# TABLE OF CONTENTS

| 1. System Outline                       |       | . 1 |  |

|-----------------------------------------|-------|-----|--|

| 1.1 Construction of System Board        | • • • | . 1 |  |

| 1.2 Block Diagram                       | • • • | . 2 |  |

| 1.3 Parts Layout                        |       | . 4 |  |

| 1.3.1 MAIN Board                        | • • • | . 4 |  |

| 1.3.2 MEMORY Board                      | •••   | . 5 |  |

| 1.3.3 FDC Board                         | • • • | . 6 |  |

| 1.3.4 List of Parts on Boards           | •••   | . 7 |  |

| 1.4 Pin Assignment of Connectors (MAIN) | •••   | . 8 |  |

| 1.4.1 LCD Connector                     | •••   | . 8 |  |

| 1.4.2 Key Board Connector               | • • • | . 8 |  |

| 1.4.3 Power Connector                   | • • • | . 9 |  |

| 1.4.4 FDD Power Connector               | •••   | . 9 |  |

| 1.4.5 SP Connector                      | • • • | . 9 |  |

| 1.4.6 MEMORY PWB Connector              | • • • | . 9 |  |

| 1.4.7 LED Indicator Connector           |       | 11  |  |

| 1.5 Pin Assignment of Connectors (FDC)  |       | 12  |  |

| 1.5.1 FDC PWB Connector                 | • • • | 12  |  |

| 1.5.2 Floppy Disk Drive Connector       | •••   | 14  |  |

| 2. Explanation of IC and I/O            | •••   | 15  |  |

| 2.1 Processor (CPU)                     | • • • | 15  |  |

| 2.2 Clock Pulse Generator               | •••   | 18  |  |

| 2.3 System Timer                        |       | 19  |  |

- i -

| 2.4  | Interrupt Controller 23                                  |

|------|----------------------------------------------------------|

| 2.5  | Direct Memory Access (DMA) Controller                    |

| 2.6  | Random Access Memory (RAM) Region 38                     |

| 2.7  | Read Only Memory (ROM) Region 40                         |

| 2.8  | Floppy Disk Drives (FDDs) 42                             |

| 2.9  | Floppy Disk Controller (FDC) 44                          |

| 2.1  | ) External Floppy Disk Controller (EXT FDC) Interface 49 |

| 2.1  | Real-Time Clock 52                                       |

| 2.1  | 2 Outline of Gate Arrays 59                              |

| 2.1  | 3 Liquid Crystal Display (LCD) 76                        |

| 2.1  | 4 Liquid Crystal Display (LCD) Controller                |

| 2.1  | 5 CRT Display Interface 103                              |

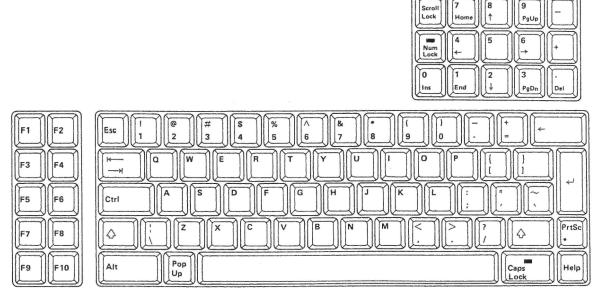

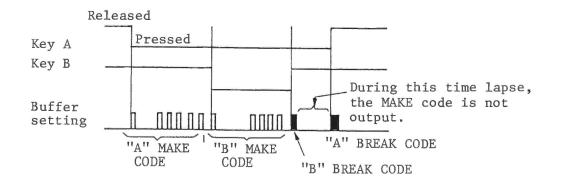

| 2.10 | 5 Keyboard and Keyboard Controller 104                   |

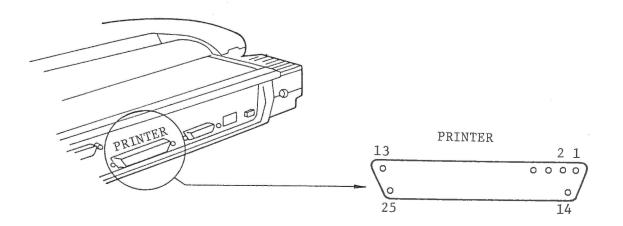

| 2.1  | 7 Printer Interface 109                                  |

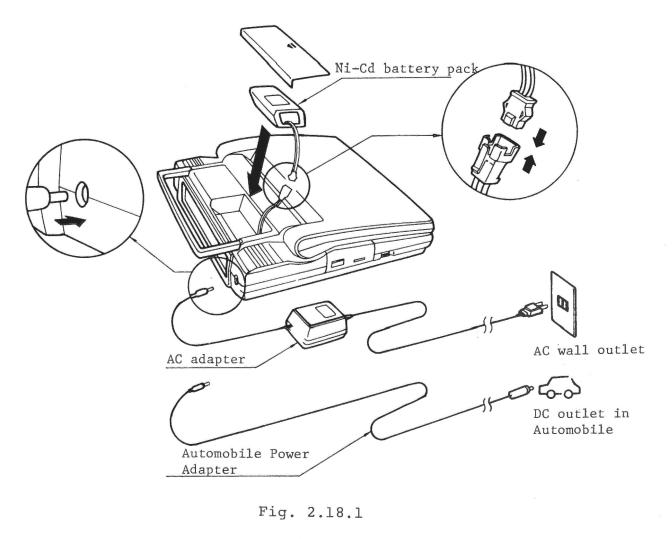

| 2.18 | B Power Supply 111                                       |

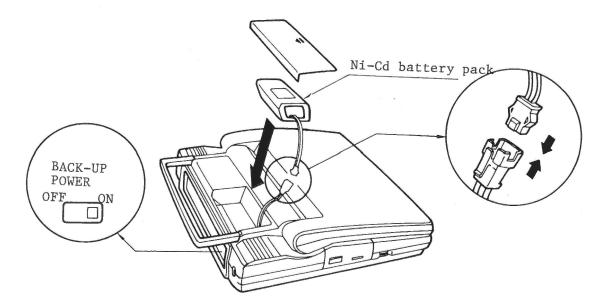

| 2.19 | Ni-Cd Battery Pack and Back-up Battery 112               |

| 2.20 | ) AC Adapter 113                                         |

| 3. ( | Option Cables 114                                        |

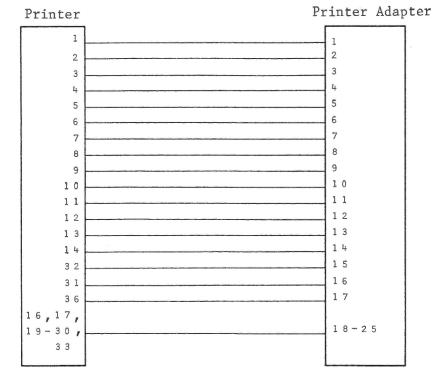

| 3.1  | Printer Cable 114                                        |

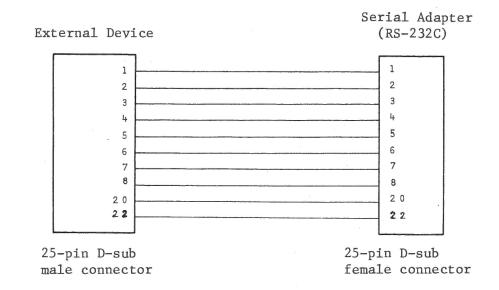

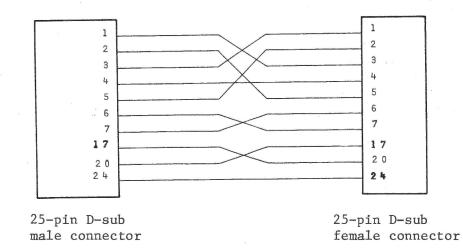

| 3.2  | RS-232C Cable 115                                        |

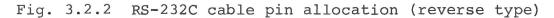

| 3.3  | External FDC Cable 117                                   |

| 3.4  | Automobile Power Cable 118                               |

•

| Appen | dix Logic Timing Diagrams   | 119 |

|-------|-----------------------------|-----|

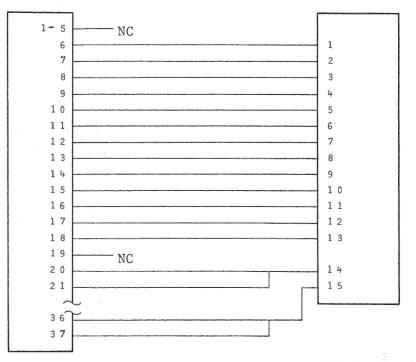

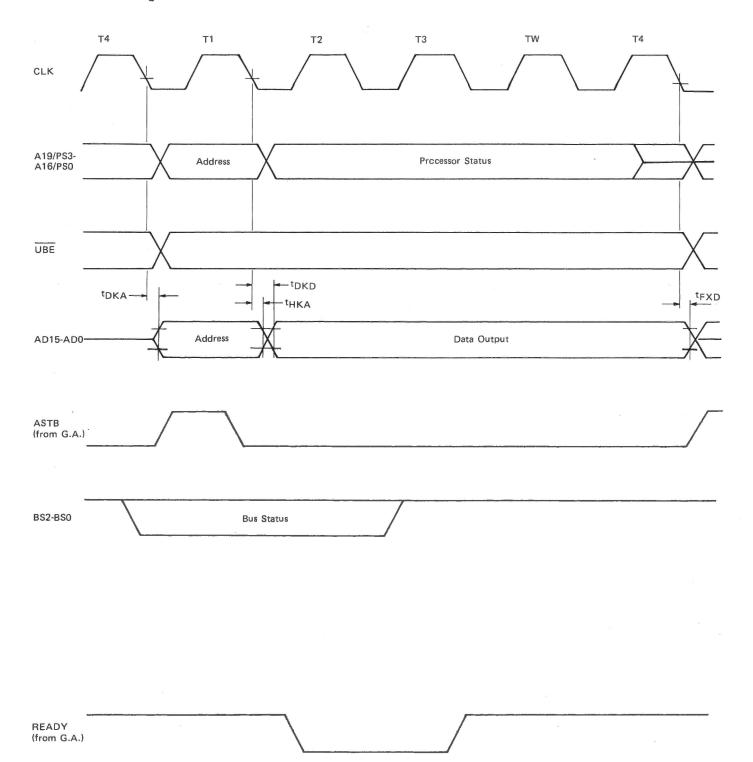

| 1.    | CPU Interface               | 120 |

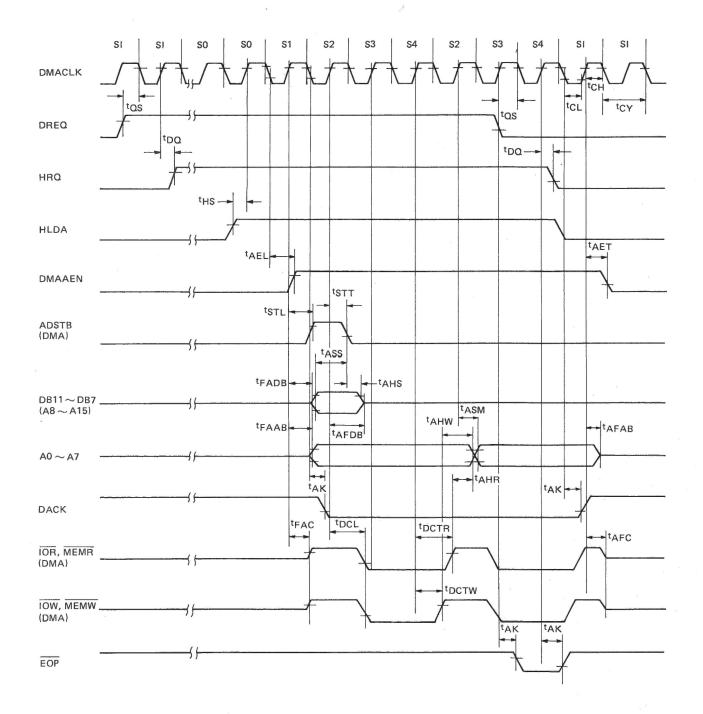

| 2.    | DMA Data Transfer Interface | 123 |

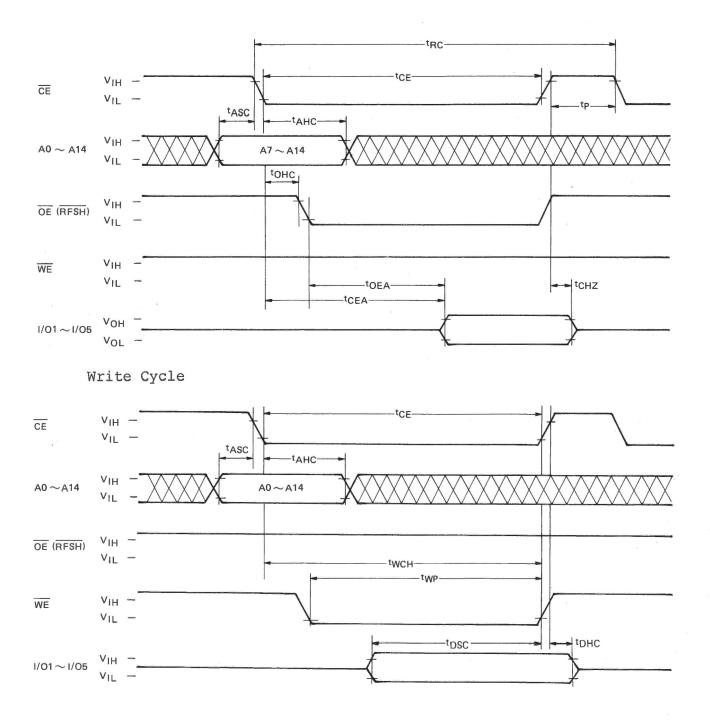

| 3.    | Memory Interface            | 125 |

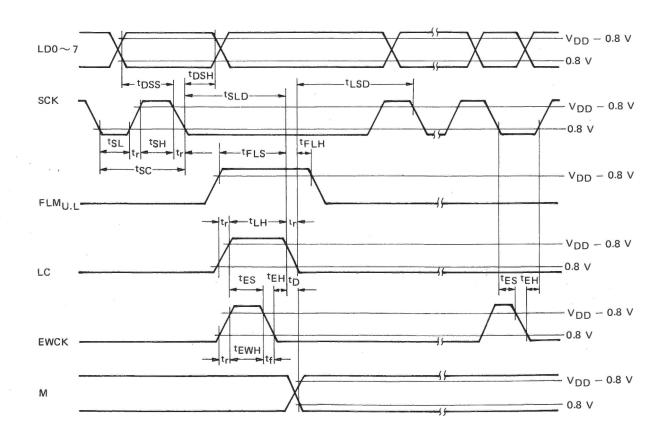

| 4.    | LCD Interface               | 127 |

а. .

#### 1. System Outline

This manual mainly explains the MultiSpeed hardware features so that MultiSpeed users can figure out the basic concept of its architecture.

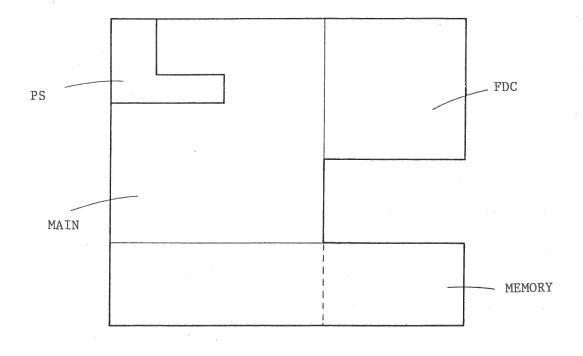

#### 1.1 Construction of System Board

The MultiSpeed system unit board is divided into four sections called the main section, memory section, FDC (floppy disk controller) section, and PS (power supply) section, as follows:

| • Main section:   | MultiSpeed's core board which comprises    |

|-------------------|--------------------------------------------|

|                   | the CPU, timer, interrupt controller, etc. |

| • Memory section: | Board which comprises main RAMs and ROMs   |

| • FDC section:    | Board which comprises the FDC, DMA         |

|                   | controller, etc.                           |

| • PC section:     | Board which supplies necessary power       |

|                   |                                            |

levels.

These four sections PC boards (printed-circuit boards) must all be connected mutually and correctly; otherwise, the MultiSpeed will malfunction. Pin assignment for the connectors which connect these PC boards are described later.

- 1 -

Fig. 1.1 System board layout

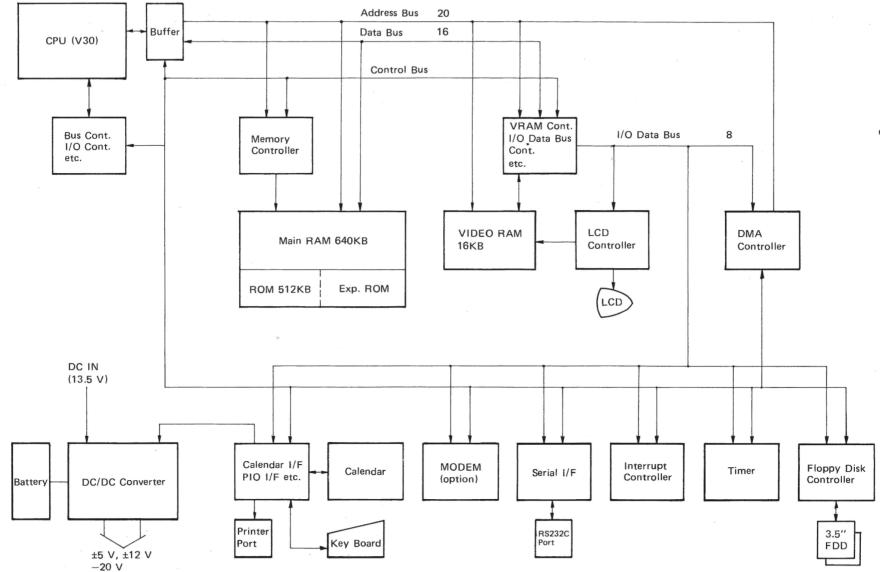

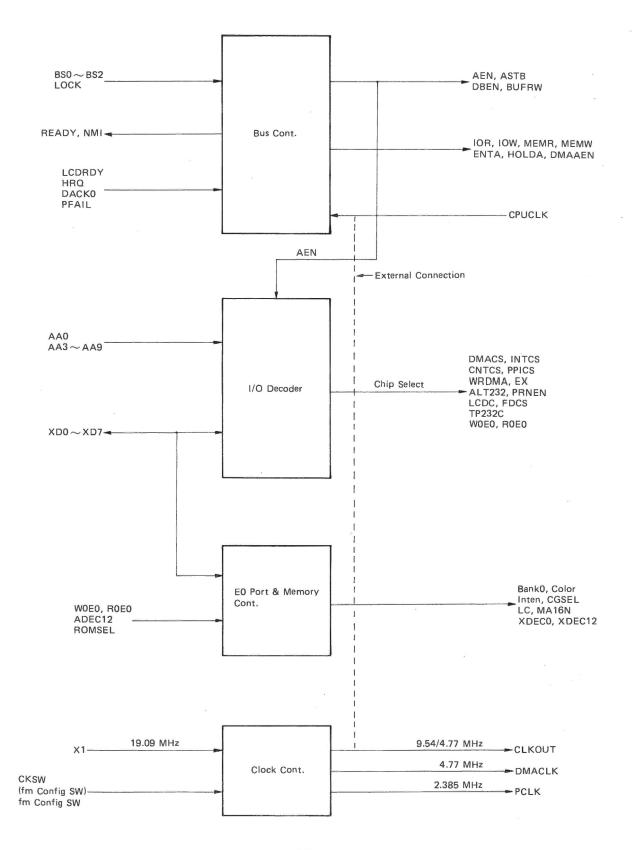

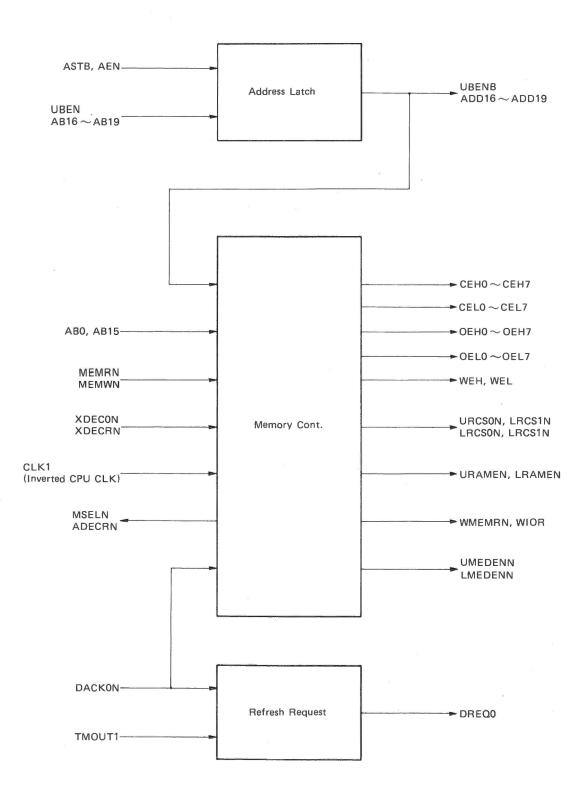

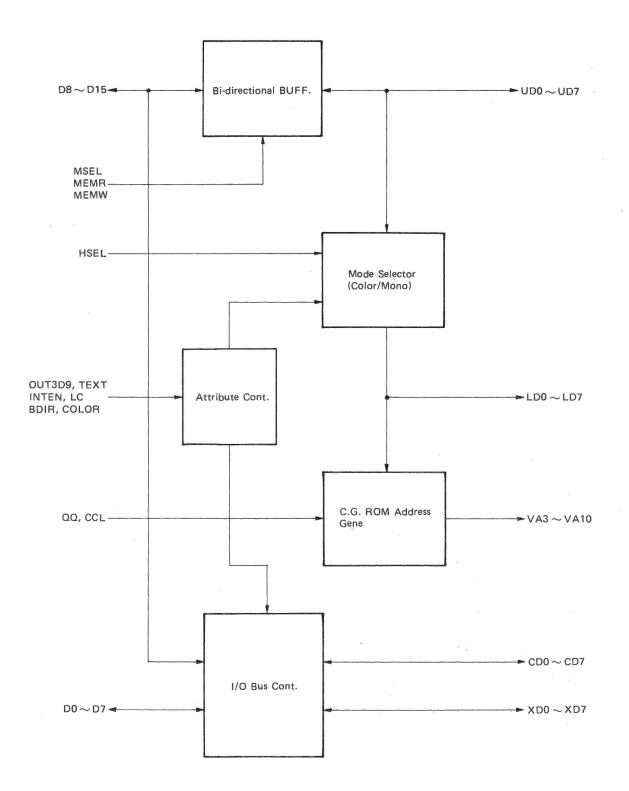

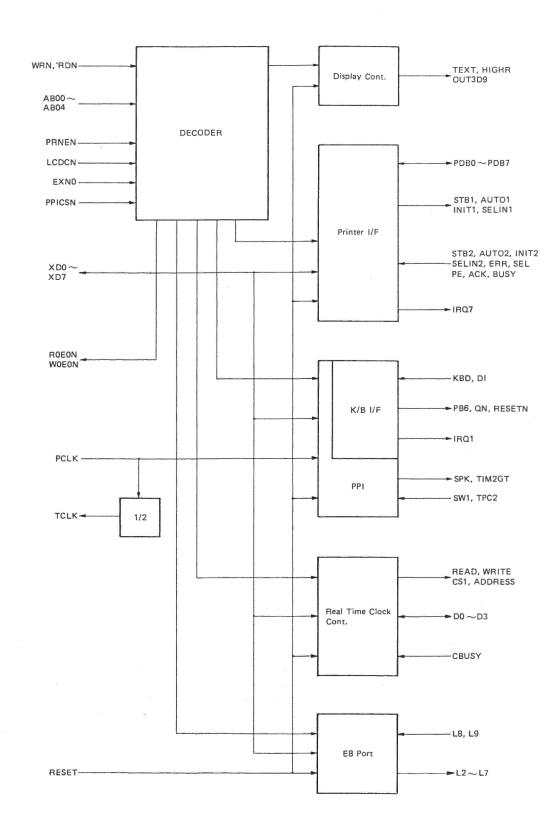

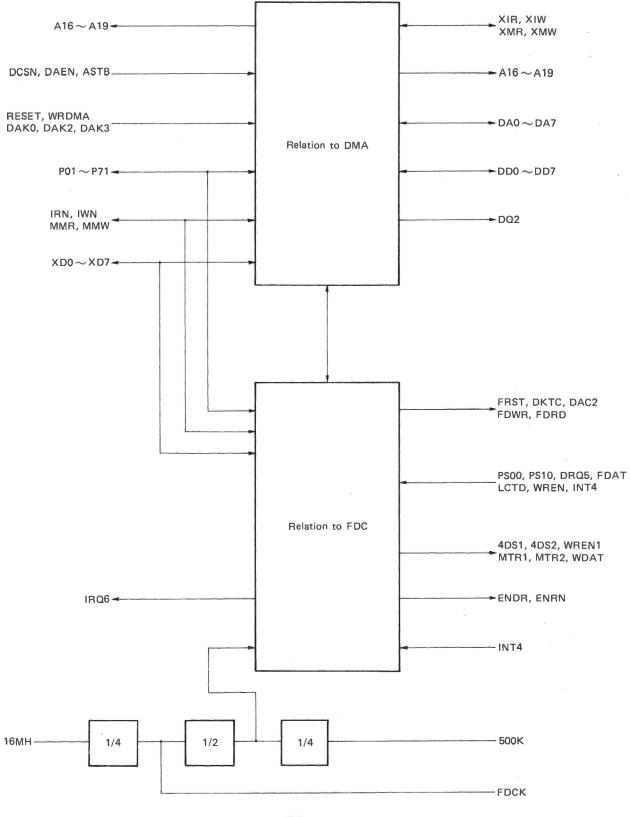

1.2 Block Diagram

ι ω

I

- 1.3 Parts Layout

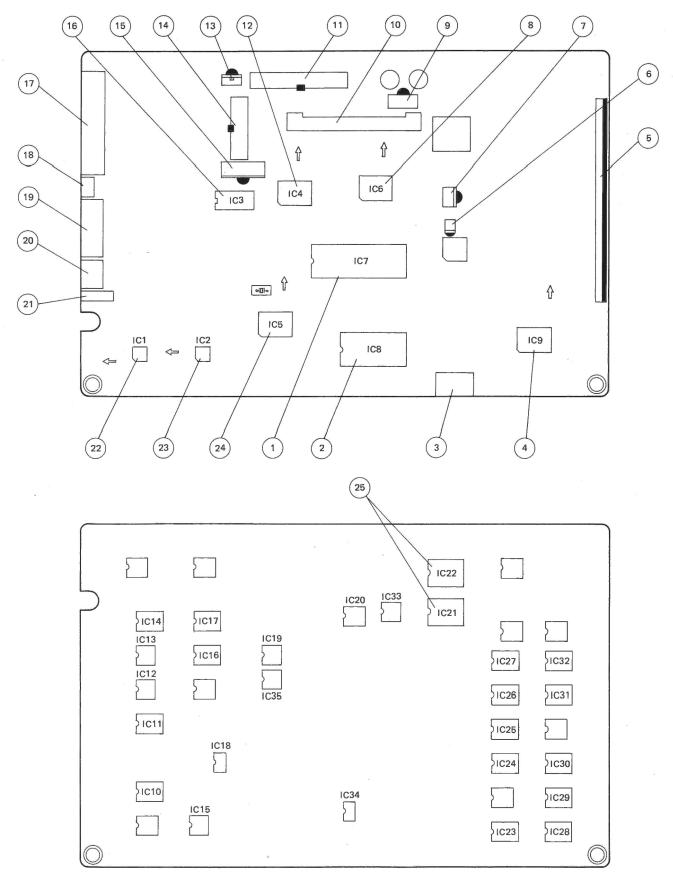

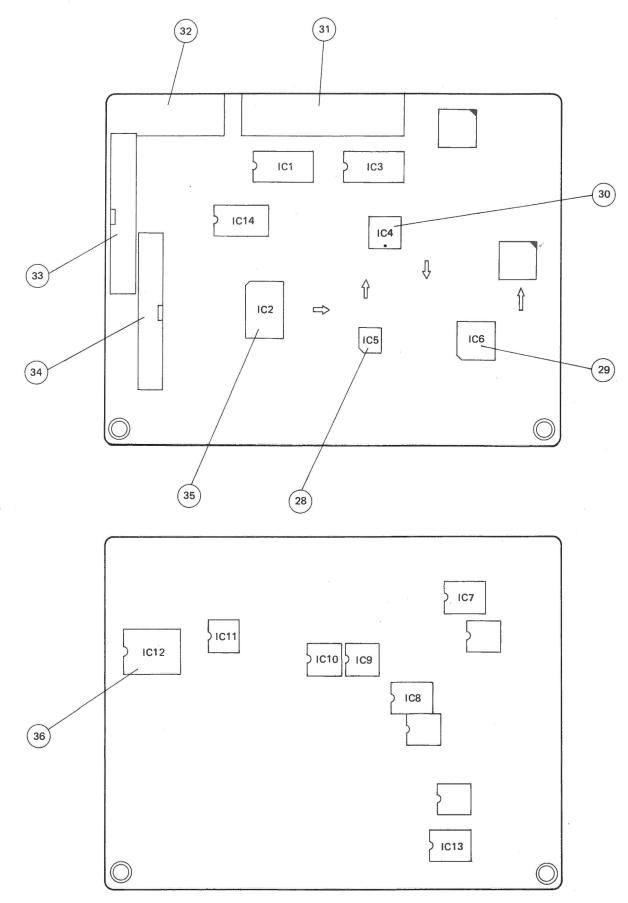

- 1.3.1 MAIN Board

- 4 -

### 1.3.2 MEMORY Board

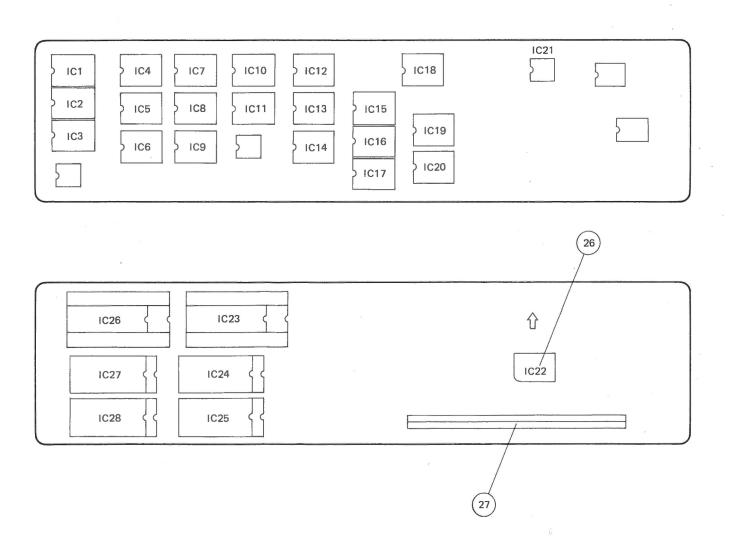

1.3.3 FDC Board

- 6 -

#### 1.3.4 List of Parts on Boards\*

- Processor µPD70116-10

- (2) Character Generator ROM

- 3 Power SW

(1)

(9)

(13)

- 4 GATE ARRAY SLA6170FIJ

- (5) MAIN-MEMORY Connector

- (6) Speaker Connector

- (7) LED Connector

- (8) GATE ARRAY SLA6170FIK

**KEY BOARD Connector**

- (10)MODEM Connector

- (11)MAIN-FDC Connector

- (12)GATE ARRAY SLA6170FIL

- FDD POWER Connector

- (14)LCD Panel Connector

- (15) POWER SUPPLY Connector

- (16)Real Time Clock RTC 58321

- (17) PRINTER Connector

- (18)Backup Battery SW

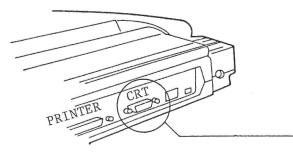

- (19) CRT Connector

- (20)Configuration SW

- \* The numbers in front of part names correspond to the numbers shown in the figures of 1.3.1 to 1.3.3.

- (21)RESET SW

- (22)Interrupt Controller uPD71059

- (23)Timer Counter uPD71054

- (24)LCD/CRT Controller V6355

- (25) VRAM

- (26) GATE ARRAY SLA6170FIM

- (27) MAIN-MEMORY Connector

- (28)DMA Controller 82C37-5

- (29) Floppy Disk Controller uPD72065

- (30)Asynchronous Communication Element 82C50

- (31) RS-232C Connector

- (32)EXT-FDC Connector

- (33)FDD Connector

- (34)MAIN-FDC Connector

- (35) GATE ARRAY µPD65013G-096

# 1.4 Pin Assignment of Connectors (MAIN)

\* The direction of I/O of each pin is based on the MAIN Board.

| Pin number                                                                                            | Signal name                                                                                                                      | I/O                                     | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | UDO<br>UD1<br>UD2<br>UD3<br>ECLK<br>FLMU<br>DF<br>LOAD<br>CP<br>LD0<br>LD1<br>LD2<br>LD3<br>FLML<br>+5<br>Vss<br>-15<br>FG<br>L5 | 000000000000000000000000000000000000000 | Vemarks<br>Upper Screen Data 0<br>Upper Screen Data 1<br>Upper screen Data 2<br>Upper Screen Data 3<br>Chip Enable<br>Upper Screen Frame Signal<br>AC Signal for Liquid Cristal<br>Data Latch<br>Data Shift<br>Lower Screen Data 0<br>Lower Screen Data 1<br>Lower Screen Data 2<br>Lower Screen Frame Signal<br>Power Supply for Logic Drive<br>Ground<br>Power Supply for Liquid Cristal<br>Frame Ground (connected No.16 Pin)<br>Reserved |

| 20                                                                                                    | L4                                                                                                                               | 0                                       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                     |

1.4.1 LCD Connector

1.4.2 Key Board Connector

| Pin number | Signal name | I/0 | Remarks                                     |

|------------|-------------|-----|---------------------------------------------|

| 1          | KBD         | 1/0 | Serial Data Line to sub CPU on the Keyboard |

| 2          | DI          |     | DATA Enable                                 |

| 3          | RESET       |     | Reset to sub CPU                            |

| 4          | GND         |     | Ground                                      |

| 5          | +5          |     | Power Supply                                |

# 1.4.3 Power Connector

| Pin number                           | Signal name                                                 | I/0 | Remarks                                                                                                                                                                                                                            |

|--------------------------------------|-------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | GND<br>-20<br>-12<br>+12<br>-5<br>+5<br>REMOTE<br>BB CHARGE | O   | Ground<br>Power Supply for LCD<br>Power Supply for RS232C and MODEM<br>Power Supply for RS232C and MODEM<br>Power Supply for MODEM<br>Power Supply for Logic Circuits<br>enable PS Board<br>Power Supply for Backup Battery Charge |

1.4.4 FDD Power Connector

| Pin number | Signal name | Remarks              |

|------------|-------------|----------------------|

| 1          | +5          | Power Supply for FDD |

| 2          | GND         | Ground               |

| 3          | GND         | Ground               |

| 4          | +5          | Power Supply for FDD |

# 1.4.5 SP Connector

| Pin number | Signal name | Remarks                    |

|------------|-------------|----------------------------|

| 1          |             | Amplified Audio Output (-) |

| 2          | +           | Amplified Audio Output (+) |

1.4.6 MEMORY PWB Connector

| Pin | number           | Signal name              | I/0         | Remarks                |

|-----|------------------|--------------------------|-------------|------------------------|

|     | 1<br>2<br>3<br>4 | NA1<br>NA2<br>NA3<br>NA4 |             | Address Bus for Memory |

|     | 5<br>6<br>7      | MA5<br>MA6<br>MA7        | 0           |                        |

|     | 8<br>9<br>10     | MA8<br>MA9<br>MA10       | 0<br>0<br>0 | <b>1</b>               |

9

| Pin number | Signal name | I/0 | Remarks                                                          |

|------------|-------------|-----|------------------------------------------------------------------|

| 11         | MA11        | 0   | <u>↑</u>                                                         |

| 12         | MA12        | 0   | 1                                                                |

| 13         | MA13        | Ō   | *                                                                |

| 14         | NA14        | 0   |                                                                  |

| 15         | NA15        | 0   |                                                                  |

| 16         | UBE         | 1   |                                                                  |

|            |             | 0   | Upper Byte Enable (-)                                            |

| 17         | A15         | 0   | Address Bus from CPU Directly                                    |

| 18         | A16         | 0   |                                                                  |

| 19         | A17         | 0   | 1 1                                                              |

| 20         | A18         | 0   | 1 1                                                              |

| 21         | A19         | 0   | 1 1                                                              |

| 22         | AO          | 0   | Address Bit O (LSB)                                              |

| 23         | ADD16       | I   | Latched Upper Bus                                                |

| 24         | ADD17       | I   | <b>*</b>                                                         |

| 25         | ADD18       | I   |                                                                  |

| 26         | ADD19       | I   |                                                                  |

| 27         | UBEN        | Ī   | Latched Upper Byte Enable (-)                                    |

| 28         | LBANKO      | Ó   | External ROM Bank Select                                         |

| 29         | HRA16       | l o | External ROM Bank Select                                         |

| 30         | BANKO       | 0   | inverted BANK SELECT BIT 0 in Port EOh                           |

|            |             |     |                                                                  |

| 31         | MA16N       | 0   | inverted Memory Address Bit 16                                   |

| 32         | MA16        | 0   | Memory Address Bit 16                                            |

| 33         | EXRCS1      | 0   | External ROM Chip Select 1                                       |

| 34         | EXRCS2      | 0   | External ROM Chip Select 2                                       |

| 35         | AEN         | 0   | Address Enable                                                   |

| 36         | ASTB        | 0   | Address Strobe                                                   |

| 37         | IOR         | 0   | I/O Read                                                         |

| 38         | WIOR        | I   | Wide I/O Read                                                    |

| 39         | CLKN        | 0   | inverted System Clock                                            |

| 40         | MSEL        | 0   | Memory Select                                                    |

| 41         | OUT1        | 0   | OUT Signal from Timer (for Memory Refresh)                       |

| 42         | DRQO        | l o | DMA Request Channel O (for Memory Refresh)                       |

| 43         | UNDEN       | Ō   | Upper Memory Data Enable                                         |

| 44         | LMDEN       | 0   | Lower Memory Data Enable                                         |

| 45         | DACKO       | I   | -                                                                |

| 46         | XDECO       | Ó   | DNA Acknowledge Channel O for Memory Refre<br>ROM Bank #O Select |

| 40         | XDECR       | 0   |                                                                  |

| 47         | ADECR       | I   | ROM Bank #1,#2 Select                                            |

|            |             | 1   | Decoded Upper Address                                            |

| 49         | WNEMR       | I   | Wide Memory Read                                                 |

| 50         | MEMR        | 0   | Memory Read                                                      |

| 51         | MENW        | 0   | Memory Write                                                     |

| 52         | MDO         | I/0 | Data Bus for Memory                                              |

| 53         | MD1         | I/0 | 1                                                                |

| 54         | MD2         | I/0 | 1                                                                |

| 55         | MD3         | I/0 | 1 1                                                              |

| 56         | MD4         | I/0 | <b>↑</b>                                                         |

| 57         | MD5         | I/0 | <b>↑</b>                                                         |

| 58         | MD6         | I/0 | 1                                                                |

| 59         | MD7         | 1/0 |                                                                  |

|            | MD8         | I/0 |                                                                  |

| Pin number                                                             | Signal name                                                                              | I/0                                                       | Remarks                                                                                                                                  |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Pin number<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68<br>69<br>70 | Signal name<br>MD9<br>MD10<br>MD11<br>MD12<br>MD13<br>MD14<br>MD15<br>MEMRST<br>+5<br>+5 | I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>O | Remarks                                                                                                                                  |

| 71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>79<br>80               | +5<br>+5<br>B+5<br>GND<br>GND<br>GND<br>GND<br>GND<br>NC<br>NC                           |                                                           | Power Supply<br>Power Supply<br>Power Supply for Memory Backup<br>Power Supply for Memory Backup<br>Ground<br>Ground<br>Ground<br>Ground |

1.4.7 LED Indicator Connector

| Pin number | Signal name | Remarks                              |

|------------|-------------|--------------------------------------|

| 1          | LED1        | Floppy Disk Drive A Select indicator |

| 2          | LED2        | Froppy Disk Drive B Select indicator |

| 3          | LED3        | Low power indicator                  |

| 4          | +5          | Power Supply                         |

1.5 Pin Assignment of Connectors (FDC)

The Direction of I/O of each pin is based on the FDC Board.

| T.D.T TEC IND CONNECCEO | 1 | .5.1 | FDC | PWB | Connector |  |

|-------------------------|---|------|-----|-----|-----------|--|

|-------------------------|---|------|-----|-----|-----------|--|

| Pin number | Signal name | I/0 | Remarks                                      |

|------------|-------------|-----|----------------------------------------------|

| Å1         | GND         |     | Ground                                       |

| A2         | GND         |     | Ground                                       |

| A3         | +5          |     | Power Supply                                 |

| A4         | A+5         |     | Power Supply for Analog Circuits             |

| A5         | -12         |     | Power Supply for RS232C                      |

| A6         | A1          | 0   | Latched I/O Address Bus                      |

| Δ7         | A3          | 0   | ↑ · · ·                                      |

| 84         | A5          | 0   | <b>†</b>                                     |

| 89         | Α7          | 0   | · †                                          |

| A10 .      | A9          | 0   | <b>†</b>                                     |

| A11        | A11         | 0   | ↑ f                                          |

| A12        | A13         | 0   | 1                                            |

| A13        | A15         | 0   | 1                                            |

| Å14        | ADD17       | 0   | î.                                           |

| A15        | ADD19       | 0   | ↑ (                                          |

| Å16        | AEN         | 0   | Address Enable                               |

| A17        | HRQ         | I   | Hold Request                                 |

| A18        | DNACLK      | 0   | Clock for DMA Controller (4.77MHz)           |

| A19        | WRDMA       | 0   | enable Data Bus to write to I/O when in DMA  |

| A20        | COM1        | 0   | Serial I/F Chip Select (RS232C)              |

| A21        | XD1         | I/0 | 8 Bits Data Bus for I/O Devices              |

| A22        | XD3         | I/0 | 1                                            |

| A23        | XD5         | I/0 | 1                                            |

| A24        | XD7         | I/0 | 1                                            |

| A25        | MENW        | 0   | Memory Write from CPU                        |

| A26        | IOW         | 0   | I/O Write from CPU                           |

| A27        | DRQO        | I   | DMA Request Channel O (for Memory Refresh)   |

| A28        | DRQ2        | I   | DMA Request Channel 2 (Floppy Disk Control)  |

| A29        | DACKO       | 0   | DMA Acknowledge Channel O for Memory Refresh |

| A30        | DACK2       | 0   | DMA Acknowledge Channel 2 for FD Control     |

| A31        | LCDRDY      | 0   | WAIT to CPU when LCD Controller is active    |

| A32        | IRQ6        | I   | Interrupt Request #6 (for FDC)               |

| A33        | NC          |     | No Connection                                |

| A34        | LED1        | 0   | Floppy Disk Drive A Select                   |

| Pin number | Signal name | I/0 | Remarks                            |

|------------|-------------|-----|------------------------------------|

| B1         | GND         |     | Ground                             |

| B2         | GND         |     | Ground                             |

| B3         | +5          |     | Power supply                       |

| B4         | +12         |     | Power supply for RS232C            |

| B5         | AO          | 0   | Latched I/O Address Bus            |

| B6         | A2          | 0   | ↑ 1                                |

| B7         | A4          | 0   | 1                                  |

| B8         | <b>A</b> 6  | 0   | ↑ ↑                                |

| B9         | 84          | 0   | t t                                |

| B10        | A10         | 0   | 1                                  |

| B11        | <b>▲</b> 12 | 0   | 1                                  |

| B12        | <b>Å</b> 14 | 0   | t t                                |

| B13        | ADD16       | 0   | t t                                |

| B14        | ADD18       | 0   | 1                                  |

| B15        | UBEN        | 0   | Latched Upper Byte Enable          |

| B16        | DMAAEN      | 0   | DMA Address Enable                 |

| B17        | HOLDA       | 0   | Hold Acknowledge                   |

| B18        | DMACS       | 0   | DMA Controller Chip Select         |

| B19        | FDCS        | 0   | Floppy Disk Controller Chip Select |

| B20        | XDO         | I/0 | 8 Bits Data Bus for I/O Devices    |

| B21        | XD2         | I/0 | 1                                  |

| B22        | XD4         | I/0 | 1                                  |

| B23        | XD6         | I/0 | 1                                  |

| B24        | MEMR        | 0   | Memory Read from CPU               |

| B25        | IOR         | 0   | I/O Read from CPU                  |

| B26        | CPURST      | 0   | System Reset                       |

| B27        | DRQ1        | I   | DMA Request Channel 1              |

| B28        | DRQ3        | I   | DMA Request Channel 3              |

| B29        | DACK1       | 0   | DMA Acknowledge Channel 1          |

| B30        | DACK3       | 0   | DMA Acknowledge Channel 3          |

| B31        | IRQ4        | I   | Interrupt Request #4 (RS232C)      |

| B32        | NC          |     | No Connection                      |

| B33        | NC          |     | No Connection                      |

| B34        | LED2        | 0   | Floppy Disk Drive B Select         |

1.5.1 FDC PWB Connector (continued)

| Pin number | Signal name | I/0 | Remarks                                   |

|------------|-------------|-----|-------------------------------------------|

| 1          | NC          |     | No Connection                             |

| 2          | NC          |     | No Connection                             |

| 3          | GND         |     | Ground                                    |

| 4          | NC          |     | No Connection                             |

| 5          | GND         |     | Ground                                    |

| 6          | +LED        | 0   | lights on LED when Drive Selected         |

| 7          | GND         |     | Ground                                    |

| 8          | IDX         | 0   | Index(min.1ms Low level Pulse)            |

| 9          | GND         |     | Ground                                    |

| 10         | -DS         | 0   | Drive Select                              |

| 11         | GND         |     | Ground                                    |

| 12         | NC          |     | No Connection                             |

| 13         | GND         |     | Ground                                    |

| 14         | NC          |     | No Connection                             |

| 15         | GND         |     | Ground                                    |

| 16         | -MTR        | 0   | Motor ON                                  |

| 17         | GND         |     | Ground                                    |

| 18         | DIR         | 0   | Direction of Head Seek                    |

| 19         | GND         |     | Ground                                    |

| 20         | STEP        | 0   | Step Pulse(min.1ms Low level pulse)       |

| 21         | GND         |     | Ground                                    |

| 22         | WD          | 0   | Write Date                                |

| 23         | GND         |     | Ground                                    |

| 24         | -WREN       | 0   | Write Enable                              |

| 25         | GND         |     | Ground                                    |

| 26         | -TKO        | 0   | Track O                                   |

| 27         | GND         |     | Ground                                    |

| 28         | -WP         | 0   | Write Protect                             |

| 29         | GND         |     | Ground                                    |

| 30         | RDIN        | I   | Read Date                                 |

| 31         | GND         |     | Ground                                    |

| 32         | HS          | 0   | Head Select."L"when head1(upper)selected. |

| 33         | GND         |     | Ground                                    |

| 34         | -RDY        | 0   | Ready                                     |

1.5.2 Floppy Disk Drive Connector (Same A and B)

\* A is the terminal for drive A and B for drive B.

#### 2. Explanation of IC and I/O

#### 2.1 Processor (CPU)

The MultiSpeed employs a  $\mu$ PD70116D-10 16-bit microprocessor. This processor has a 16-bit data bus and a 20-bit address bus, supporting the IM-byte address space.

This processor has two built-in 16-bit data buses. This processor operates these two buses in parallel, to reduce the number of processing steps required to execute instructions. This processor, besides, is provided with a built-in EAG (effective address generator), which enables high-speed calculation of effective addresses in all addressing modes, which is required for memory accessing. This processor, moreover, has a 16/32-bit temporary register/shifter (hardware) to process multiplication, division, and shift/rotation instructions for the purpose of higher processing.

The user can select as this processor clock frequency 4.77 MHz or 9.54 MHz.

#### \* Programming considerations

This processor uses four 16-bit general registers, AX, BX, CX, and DX. Each can be used as a 16-bit register and can also be divided into two 8-bit registers of highorder and low-order (AH, AL, BH, BL, CH, CL, DH, and DL). Those general registers can also be used as the default register to process special instructions as shown in Fig. 2.1.1 below.

Fig. 2.1.1 Default registers

| AX | Word multiplication/division, word input/<br>output, interpretation, BCD (binary coded<br>decimal) rotation, data conversion |

|----|------------------------------------------------------------------------------------------------------------------------------|

| AL | Byte multiplication/division, byte input/output,<br>BCD rotation, byte conversion                                            |

| АН | Byte multiplication/division                                                                                                 |

| BX | Interpretation                                                                                                               |

| СХ | Loop control branch, repeat prefix                                                                                           |

| CL | Shift instruction, rotation instruction, BCD operation                                                                       |

| DX | Word multiplication/division, indirect address-<br>ing input/output                                                          |

Besides those general registers, this processor has a 16-bit register called program status word. This register consists of two flags: control flag which controls processor operation and status flag which automatically changes based on the result of instruction execution so as to indicate the system status.

The control flag comes in four types: MD (mode), DIR (direction), IE (interrupt enable), and BRK (break);

while the status flag comes in six types: V (overflow), S (sign), Z (zero), AC (auxiliary carry), P (parity), and CY (carry). Out of these, the CY flag can directly be set, reset, and reversed by instructions. These flags are arrayed on the program status word in the configuration shown in Fig. 2.1.2.

| 15     | 14 | 13 | 12 | 11 | 10          | 9      | 8           | 7 | 6 | 5 | 4      | 3 | 2 | 1 | 0      |

|--------|----|----|----|----|-------------|--------|-------------|---|---|---|--------|---|---|---|--------|

| M<br>D | 1  | 1  | 1  | v  | D<br>I<br>R | I<br>E | B<br>R<br>K | s | Z | 0 | A<br>C | 0 | P | 1 | C<br>Y |

Fig. 2.1.2 Program status word

#### 2.2 Clock Pulse Generator

This clock pulse generator is built in the IC SLA6170FIK gate array to generate the clock pulse used by the processor or other devices. This clock pulse may come in a frequency of 4.77 MHz or 9.54 MHz, which can be switched by turning bit 4 of the dip switch on the rear panel of the MultiSpeed body on and off respectively. Moreover, when bit 4 of the dip switch is set to off to provide a frequency of 9.54 MHz, the clock frequency can be switched by software.

This clock pulse generator divides the source frequency of 19.090906 MHz by four into 4.77 MHz and by two into 9.54 MHz. Both frequencies have the same duty ratio of 50%.

#### \* Programming considerations

To switch the clock frequency by software, the abovementioned dip switch (bit 4) must be set to OFF (9.54 MHz) beforehand. Then, the operator can switch the frequency by setting or resetting the MSB (D7) of the clock/character generator (CG)/ROM mapping register in I/O address E0 (hex). By setting the MSB to 0, the clock frequency is switched to 4.77 MHz, and by setting it to 1, 9.54 MHz.

The other bits of this register are detailed later.

#### 2.3 System Timer

As the system timer this processor employs a µPD71054 programmable timer counter. This timer has three counters which operate mutually independently: counter #0 as software interrupt counter, counter #1 to control the refresh timing for the direct memory access controller, and counter #2 to support the tone generator for the speaker.

These three built-in counters use the same clock frequency obtained by dividing a frequency of 4.77 MHz by two. With this, those counters have the same minimum timing resolution of 420 nsec.

#### \* Programming considerations

This system timer can be programmed by writing both the control word which specifies the operation mode of each built-in counter and the upper limit count value. With this, those built-in counters operate as a countdown counter.

Before use, first specify the desired operation mode of each counter with the control word. A mode once programmed into the counter remains unchanged until it is switched to a different one.

- 19 -

Next, write a count value to the count register for each counter. Immediately after the count value thus written is transferred from the count register to the down counter, it starts counting.

The control word must be written to I/O address 043 (hex) and the count value, to 040(hex) through 042(hex).

The operator can read out the current count data during counting. To do so, he must use the count latch command or multiple latch command. With this, he can read it out without affecting timer operation.

Some bits of the 061(hex) port B or 062(hex) port C are used to stop, start, and detect the output of the counting by counter #2 (for tone generator).

| Address (hex) | R/W | Usage                       |

|---------------|-----|-----------------------------|

| 040           | R/W | Counter #0                  |

| 041           | R/W | Counter #1                  |

| 042           | R/W | Counter #2                  |

| 043           | W   | Timer control word register |

| 061           | W   | Port B                      |

| 062           | R   | Port C                      |

Fig. 2.3.1 Timer control register

| Timer | Control | Word | Register: | 043(hex) |

|-------|---------|------|-----------|----------|

|-------|---------|------|-----------|----------|

| D7  | D6  | D5   | D4   | D3  | D2  | D1  | D0  |

|-----|-----|------|------|-----|-----|-----|-----|

| SC1 | SC0 | RWM1 | RWMO | CM2 | CM1 | CM0 | BCD |

#### Bit Usage

| 7 - 6 | Counter selection or multiple latch command                                                     |

|-------|-------------------------------------------------------------------------------------------------|

|       | SC1 SC0<br>0 0: Counter #0<br>0 1: Counter #1<br>1 0: Counter #2<br>1 1: Multiple latch command |

| 5 - 4 | Read/Write mode                                                                                 |

|       | RWM1 RWM0<br>0 0: Count latch command                                                           |

| <u> </u> | ••• | oodiio zaooli oolallalla          |

|----------|-----|-----------------------------------|

| 0        | 1 : | Low-order byte read/write         |

| 1        | 0:  | High-order byte read/write        |

| 1        | 1 : | Read/write of low-order and high- |

|          |     | order bytes in this order         |

3 - 1 Count mode

| CM2 | CM1 | CM0 |      |   |

|-----|-----|-----|------|---|

| 0   | 0   | 0:  | Mode | 0 |

| 0   | 0   | 1 : | Mode | 1 |

| -   | 1   | 0 : | Mode | 2 |

|     | 1   | 1:  | Mode | 3 |

| l   | 0   | 0:  | Mode | 4 |

| 1   | 0   | 1 : | Mode | 5 |

Binary or BCD counting 0 : Binary counting (16 digits) 1 : BCD counting (4 digits) 0

Port B : 061(hex)

Some bits of the port B register are used for the system timer. The other bits are explained as required.

- Bit Usage

- 0 Enables output of the counter #2 content. Counter #2 is stopped by setting this bit to 0.

Port C : 062 (hex)

Some bits of the Port C register are used for the system timer. The other bits are explained as required.

Bit Usage

5

Counter #2 output. When this bit is detected, the application program can monitor the output of counter #2.

#### 2.4 Interrupt Controller

As the interrupt controller the MultiSpeed employs the  $\mu$ PD71059G interrupt control unit.

This programmable interrupt controller enables the operator to change the priority of interrupt requests, mask interrupts at a desired interrupt level, and set the interrupt routine address, etc. by transferring the command word from the processor. This interrupt controller is used in the edge trigger mode by the MultiSpeed.

The MultiSpeed hardware interrupt comes in eight levels of maskable interrupts (levels 0 to 7) and one nonmaskable interrupt (NMI) that cannot be masked by software. As for the priority order of those interrupt levels, the NMI has always the highest one, followed by levels 0 to 7 which can be programmed. Upon power application, the NMI is automatically given the highest priority, followed by levels 0 to 7 in this order as a result of initialization.

Levels 0 through 7, which are programmable, are of the rotating priority system, so that once the lowest level is specified, the other levels are automatically determined. Note here that interrupt levels 0 to 7 are assigned to processor interrupt vectors 8 to 15 respectively. Fig. 2.4.1 below gives the hardware interrupt levels.

- 23 -

#### Fig. 2.4.1 Hardware interrupt levels

| Interrupt | Usage                                 |  |  |  |  |  |

|-----------|---------------------------------------|--|--|--|--|--|

| NMI       | Power fail/Power switch               |  |  |  |  |  |

| 0         | Timer                                 |  |  |  |  |  |

| 1         | Keyboard                              |  |  |  |  |  |

| 2         | Reserved                              |  |  |  |  |  |

| 3         | Asynchronous Communications (RS-232C) |  |  |  |  |  |

| 4         | Asynchronous Communications (Modem)   |  |  |  |  |  |

| 5         | Reserved                              |  |  |  |  |  |

| 6         | Diskette                              |  |  |  |  |  |

| 7         | Printer                               |  |  |  |  |  |

|           |                                       |  |  |  |  |  |

### \* Programming considerations

The control words used by this interrupt controller can roughly be divided into two groups: initialize word and command word.

The initialize word comes in four types, IWl to IW4, for initialization of the interrupt controller, which requires for starting general processing that proper information should be written to those four words. In the MultiSpeed, however, IW3 is not used because the interrupt controller is not connected in a cascade.

The command word, on the other hand, comes in three types: the interrupt mask word (IMW), priority and

finish control word (PFCW), and mode control word (MCW). Those three words are used to give the necessary commands to the interrupt controller for the purpose of masking interrupt requests, changing the priority, and terminating interrupt processing.

This interrupt controller enters the initialize sequence immediately after IWl is written to I/O address 020 (hex). Immediately after IW2 and IW4 are both written to address 021 (hex), the initialization of the interrupt controller is completed.

Once the interrupt controller completely passes the initialize sequence, the operator can give command words as he likes. The IMW and the PFCW and MCW are set to addresses 021 (hex) and 020 (hex) respectively. Into address 020 (hex) appears the information of the built-in register of interrupt controller read out with the MCW. The NMI for the MultiSpeed uses some bits of address 0A0 (hex). Fig. 2.4.2 lists the interrupt and NMI control registers.

- 25 -

# Fig. 2.4.2 Interrupt and NMI control registers

| Address<br>(hex) | R/W | Usage                                   |  |  |  |  |

|------------------|-----|-----------------------------------------|--|--|--|--|

| 020              | W   | Initial word 1 (IW1)                    |  |  |  |  |

|                  | W   | Priority and finish control word (PFCW) |  |  |  |  |

|                  | w٠  | Mode control word (MCW)                 |  |  |  |  |

|                  | R   | Interrupt request register              |  |  |  |  |

|                  | R   | Interrupt in-service register           |  |  |  |  |

|                  | R   | Polling data                            |  |  |  |  |

| 021              | W   | Initial word 2 (IW2)                    |  |  |  |  |

|                  | W   | Initial word 4 (IW4)                    |  |  |  |  |

|                  | R/W | Interrupt mask word (IMW)               |  |  |  |  |

| 0A*              | W   | NMI Mask Register                       |  |  |  |  |

Note: The address marked \* is a "don't-care" one. NMI Mask Register (0A\* (hex))

The NMI (nonmaskable interrupt) occurs if the power switch is turned off or if the power voltage drops below 9.3 V. Such NMIs can be masked using some bits of the NMI mask register, as follows:

Bit Usage

7 '0': Disable NMI

'l': Enable NMI

Command Word Formats

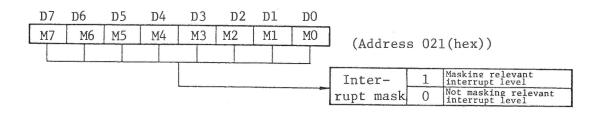

Interrupt Mask Word (IMW)

This word masks the interrupt request register (IRR) so as to inhibit interrupt requesting at the relevant interrupt level. This word also masks the interrupt in-service register (ISR) in the exception nest mode.

Fig. 2.4.3 Interrupt mask word

•Priority and Finish Control Word (PFCW)

This word is used to set the command which notifies the interrupt controller of the termination of interrupt processing or change (rotate) the interrupt request priority.

|                    | D | 7 | D6  | D5        | D4               | D3            | D2            | D1                       | DO                                |        |                                 |  |

|--------------------|---|---|-----|-----------|------------------|---------------|---------------|--------------------------|-----------------------------------|--------|---------------------------------|--|

|                    | R | P | SIL | <u>FI</u> | 0                | 0             | IL2           | IL1                      | ILO                               | (Ad    | dress 020(hex))                 |  |

|                    |   |   |     |           |                  |               | 0             | 0                        | 0                                 | 0      |                                 |  |

|                    |   |   |     |           |                  | el            | 0             | 0                        | 1                                 | 1      |                                 |  |

|                    |   |   |     |           |                  | lev           | 0             | 1                        | 0                                 | 2      |                                 |  |

|                    |   |   |     |           |                  |               | 0             | 1                        | 1                                 | 3      |                                 |  |

|                    |   |   |     |           |                  | upt           | 1             | 0                        | 0                                 | 4      |                                 |  |

|                    |   |   |     |           |                  | terrupt       | 1             | 0                        | 1                                 | 5      |                                 |  |

|                    |   |   |     |           |                  | nte           | 1             | 1                        | 0                                 | 6      |                                 |  |

|                    |   |   |     |           |                  | In            | 1             | 1                        | 1                                 | 7      |                                 |  |

|                    |   |   | +   |           |                  |               |               |                          |                                   |        |                                 |  |

| ц                  | 0 | • | 0   | 1         |                  |               | Leve          | l not                    | Not r                             | otated | General FI command              |  |

| tion<br>d          | 1 |   | 0   | 1         |                  |               | specified     |                          | Rotated                           |        | General rotation FI command     |  |

| rota               | 0 |   | 1   | 1         | FI               |               |               | Not re                   | Not rotated Specified FI command  |        |                                 |  |

| y rotat<br>command | 1 |   | 1   | 1         | comm             | command Level |               | Rota                     | Rotated Specified rotation F1 cor |        |                                 |  |

| ty<br>co           | 0 |   | 1   | 0         | New FT specified |               | Not r         | Not rotated No operation |                                   |        |                                 |  |

| LT.                | 1 |   | 1   | 0         | ]Non-            | on-FI         |               |                          | Rotated                           |        | Specified rotation command      |  |

| d Lo               | 0 |   | 0   | 0         | comm             | and           | und Level not |                          | Not rotated Se                    |        | Self-FI mode rotation resetting |  |

| Pr<br>an           | 1 |   | 0   | 0         | ]                |               | spec          | ified                    | Rota                              | ated   | Self-FI mode rotation setting   |  |

Fig. 2.4.4 Priority and Finish Control Word

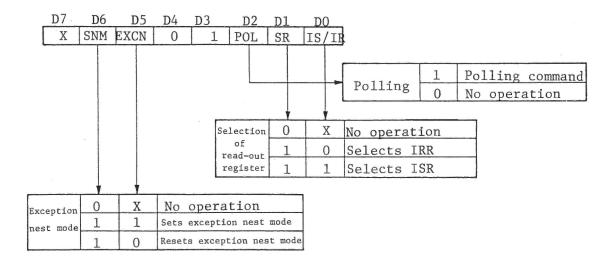

•Mode Control Word (MCW)

This word is used to make polling, set read-out registers, or set the exception nest mode.

Fig. 2.4.5 Mode control word

#### 2.5 Direct Memory Access (DMA) Controller

As the direct memory access (DMA) controller the Multi-Speed employs the 82C37-5 programmable DMA controller. This DMA controller enables high-speed data transfer because there need not be intervention by the processor over the peripherals mounted for data transfer among memory I/O devices and, moreover, it will not take in data which it transfers itself.

This DMA controller has four programmable DMA channels (channel numbers 0 to 3), each of which can be controlled independently. This DMA controller comes in three transfer modes, the single, block, and demand transfer modes, so that the operator can select and set, for each channel, auto initialize inhibition, DMA transfer inhibition, transfer address incrementing, or transfer address decrementing. Channel #0, however, is exclusively used for memory refreshing and channel #2, for DMA transfer between the floppy disk and memory.

Data transfer in the single mode requires for operation six clock pulses (1.25 ms) for each byte. Both the block mode and the demand mode require that at least three clocks (0.63 ms) each should be given for the second byte and subsequent bytes. This DMA controller uses a clock frequency of 4.77 MHz. The priority for these channels is fixed in such a way that channel #0 has the highest priority, followed by channel #1 to channel #3 in this order. This system, however, does not support either inter-memory data transfer or cascading.

#### \* Programming considerations

This DMA controller has a built-in address register of 16-bit configuration, so that it supports 20-bit addresses by providing a 4-bit page register for each DMA channel in addresses 080 (hex) through 083 (hex). Each page register is allocated to the high-order four bits of the 20-bit DMA transfer address as shown in Fig. 3.5.1. The page register for channel #0, however, cannot be used.

| 19 | 18           | 17  | 16 | 15 | 14 | 13 | 12 | 11  | 10 | 9   | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|--------------|-----|----|----|----|----|----|-----|----|-----|----|---|---|---|---|---|---|---|---|

| I  | Page<br>Tegi | ste | r  |    |    |    |    | DMA | a  | ldr | es | s |   |   |   |   |   |   |   |

|    |              |     |    |    |    |    |    |     |    |     |    |   |   |   |   |   |   |   |   |

DMA address bit configuration

Fig. 3.5.1 DMA address configuration

This DMA controller uses such registers as listed in Fig. 3.5.2, to set the DMA operation mode or transfer address and the transfer data count value or each read out channel status by use of the processor.

- 31 -

## Fig. 3.5.2 DMA controller registers

| Address<br>(hex) | R/W | Usage                                  |

|------------------|-----|----------------------------------------|

| 000              | R/W | Channel #0 current address register    |

| 001              | R/W | Channel #0 current word count register |

| 002              | R/W | Channel #1 current address register    |

| 003              | R/W | Channel #1 current word count register |

| 004              | R/W | Channel #2 current address register    |

| 005              | R/W | Channel #2 current word count register |

| 006              | R/W | Channel #3 current address register    |

| 007              | R/W | Channel #3 current word count register |

| 008              | R   | Status register                        |

|                  | W   | Command register                       |

| 009              |     | Request register                       |

| 00A              |     | Single mask register                   |

| 00B              |     | Mode register                          |

| 0 0 C            | W   | Clear first last F/F                   |

| 00D              | W   | Mask clear register                    |

| 0 0 E            | W   | Clear-mask register                    |

| 00F              | W   | All-mask register                      |

| 080              |     | Not used                               |

| 081              | W   | Channel #2 page register               |

| 082              | W   | Channel #3 page register               |

| 083              | W   | Channel #1 page register               |

DMA Command Register: 008 (hex)

Only some bits of the DMA command register can be set by the user, the other bits being automatically initialized upon system start-up.

#### Bit Usage

2 Disables the DMA controller. If this bit is set to 1, data transfer is inhibited over all DMA channels.

DMA Status Register: 008 (hex)

- Bit Usage

- 7 Channel #3 request

0: Not requested

- 1: Requested

- 6 Channel #2 request

- 0: Not requested

- 1: Requested

5 Channel #1 request

- 0: Not requested

- 1: Requested

- 4 Channel #0 request

0: Not requested

1: Requested

3 Channel #3 terminal count

- 0: Terminal count is not reached.

- 1: Terminal count is reached.

- 2 Channel #2 terminal count

0: Terminal count is not reached.

1: Terminal count is reached.

- 33 -

Channel #1 terminal count

0: Terminal count is not reached.

1: Terminal count is reached.

0 Channel #0 terminal count

0: Terminal count is not reached.

1: Terminal count is reached.

Request Register: 009 (hex)

The request register is used to make software requests like DMA requests from peripherals.

Bit

l

| 7 -    | - 3     | Not   | used  | 1     |      |      |     |      |

|--------|---------|-------|-------|-------|------|------|-----|------|

| 2      | 2       | Requ  | uest  | bit   |      |      |     |      |

|        |         | 0:    | The   | requ  | est  | is   | res | set. |

|        |         | 1:    | The   | requ  | est  | is   | set | Ξ.   |

| 1 -    | - 0     | Chai  | nnel  | spec  | ific | cati | ion | bit  |

|        |         | 00:   | Cha   | annel | #0   |      |     |      |

|        |         | 01:   | Cha   | annel | #1   |      |     |      |

|        |         | 10:   | Cha   | annel | #2   |      |     |      |

|        |         | 11:   | Cha   | annel | #3   |      |     |      |

| Single | Mask Re | egist | ter:  | 00A   | (he  | ex)  |     |      |

| Bi     | it      | Usag  | ge    |       |      |      |     |      |

| 7 -    | - 3     | Not   | used  | L     |      |      |     |      |

| 2      | 2       | Masł  | k bit | :     |      |      |     |      |

|        |         | 0:    | Mask  | ing : | is r | ese  | et. |      |

|        |         | 1:    | Mask  | ing : | is s | set. |     |      |

|        |         |       |       |       |      |      |     |      |

- 34 -

1 - 0 Channel specification

| 00: | Not used | E  |

|-----|----------|----|

| 01: | Channel  | #1 |

| 10: | Channel  | #2 |

| 11: | Channel  | #3 |

# Mode Register

The mode register is used to set the operation mode for . each channel.

| Bit   | Usage                                         |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

| 7 - 6 | Transfer mode specification                   |  |  |  |  |  |  |  |

|       | 00: Demand transfer mode                      |  |  |  |  |  |  |  |

| . *   | 01: Single transfer mode                      |  |  |  |  |  |  |  |

|       | 10: Block transfer mode                       |  |  |  |  |  |  |  |

|       | 11: Cascade mode                              |  |  |  |  |  |  |  |

| 5     | Address incrementing/decrementing             |  |  |  |  |  |  |  |

|       | 0: Address incrementing                       |  |  |  |  |  |  |  |

|       | 1: Address decrementing                       |  |  |  |  |  |  |  |

| 4     | Auto initialization permitted/not permitted   |  |  |  |  |  |  |  |

|       | 0: Auto initialization not permitted          |  |  |  |  |  |  |  |

|       | 1: Auto initialization permitted              |  |  |  |  |  |  |  |

| 3 - 2 | Transfer direction setting (transfer request) |  |  |  |  |  |  |  |

|       | 00: Verify transfer                           |  |  |  |  |  |  |  |

|       | 01: Write transfer                            |  |  |  |  |  |  |  |

|       | 10: Read transfer                             |  |  |  |  |  |  |  |

|       | ll: Transfer inhibited                        |  |  |  |  |  |  |  |

- 35 -

- 1 0 Channel specification

- 00: Channel #0

- 01: Channel #1

- 10: Channel #2

- 11: Channel #3

Clear First/Last F/F: 00C (hex)

This F/F (flip-flop) acts as a software command.

The DMA controller of the MultiSpeed transfers the content of the 16-bit address or word count register twice for the high-order eight bits and the low-order eight bits each. For this purpose, the first/last F/F is used to judge the high-order bits and the low-order bits in such a way that when this F/F is reset the low-order bits are transferred and when it is set the high-order bits are transferred. By resetting this F/F, the low-order eight bits can be accessed.

Master Clear Register: 00D (hex)

This register acts as a software command, to set the mask register and reset the contents of the command, status (low-order four bits), request, and temporary registers as well as of the first/last F/F. This master clear command,

- 36 -

when executed, permits the DMA controller to enter the idle cycle.

Clear Mask Register: 00E (hex)

This register acts as a software command. This command, when executed, resets the mask bit of all DMA channels, so that DMA transfer is accepted.

All Mask Register: 00F (hex)

This register gives a direction to permit or inhibit data transfer for all channels at a time.

| Bit   | Usag |      |    |      |

|-------|------|------|----|------|

| 7 - 4 | Not  | used | E  |      |

| .3    | Char | nnel | #3 | mask |

|       | 0:   | Rese | et |      |

|       | 1:   | Set  |    |      |

| 2     | Char | nnel | #2 | mask |

|       | 0:   | Rese | et |      |

|       | 1:   | Set  |    |      |

| 1     | Char | nnel | #1 | mask |

|       | 0:   | Rese | et |      |

|       | 1:   | Set  |    |      |

| 0     | Not  | used | E  |      |

|       |      |      |    |      |

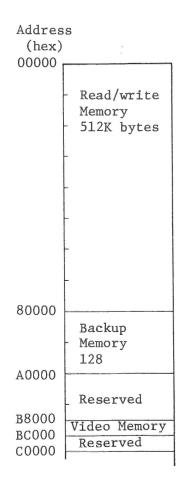

#### 2.6 Random Access Memory (RAM) Region

This RAM region comprises the 512K-byte non-backup RAM, 128K-byte backup RAM, and 16K-byte video RAM. Addresses 80,000 (hex) and subsequent are covered by the static RAM, while addresses 00,000 (hex) through 7F,FFF (hex) are covered by the pseudo-static RAM, which needs refreshing. This RAM area of the MultiSpeed does not have a parity bit.

The RAM address starts with 00,000 (hex), whose subsequent addresses are assigned as shown in Fig. 3.6.1.

#### Fig. 3.6.1 RAM map

- 38 -

### \* Programming considerations

As many as 128K bytes of addresses starting from RAM address 80,000 (hex) are allocated in the backup RAM area, which can be used only by the system. In order to not destroy the data stored in this system area, the user should not use that area.

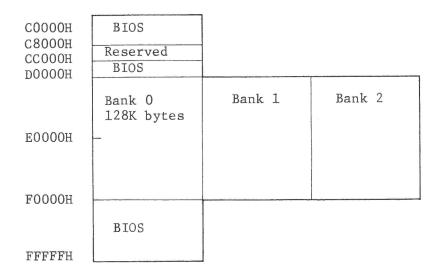

#### 2.7 Read Only Memory (ROM) Region

This ROM region comprises a 512K-byte area, to cover addresses C0,000 (hex) through FF,FFF (hex).

A ROM region area of addresses D0,000 (hex) through EF,FFF (hex), which has a capacity of 128K bytes, can be switched in three ways as a bank so as to be used as an area having a capacity of 384K bytes. By adding expansion ROM devices, this area can be extended to five banks (640K bytes), so that the ROM region can be expanded to 768K bytes as a whole.

Fig. 2.7.1 ROM map

#### \* Programming considerations

To access the intra-ROM region bank, the currently used bank must be switched to that bank desired. For bank switch-over, the CLK/CG/ROM mapping register in address OEO (hex) is used.

CLK/CG/ROM Mapping Register: 0E0 (hex)

Some bits of this register are used to specify a desired ROM bank (bank switch-over). The other bits are explained as required.

Bit Usage

| 2 | - | 0 | ROM bank # |      |     |  |  |

|---|---|---|------------|------|-----|--|--|

|   |   |   | 000:       | Bank | # O |  |  |

|   |   |   | 001:       | Bank | #1  |  |  |

|   |   |   | 010:       | Bank | #2  |  |  |

|   |   |   |            |      |     |  |  |

Oll: Bank #3 (Expansion ROM)

100: Bank #4 (Expansion ROM)

- 41 -

2.8 Floppy Disk Drives (FDDs)

The MultiSpeed employs a disk unit which comprises two floppy disk drives (FDDs) for handling 3.5-inch micro-floppy disks. Both of these drives are compatible with IBM-formatted floppy disks, supporting double-sided double-density floppy disks to provide a capacity of 720K bytes per drive after being formatted.

When a floppy disk is inserted into the slot of this floppy disk drive and set to it, the floppy disk is first chucked internally by the spindle motor, which automatically rotates. This automatic chucking takes 800 ms at most.

After the floppy disk is correctly set to the read/write drive, the spindle motor starts rotating to rotate the floppy disk. The disk rotating speed is stabilized by the frequency servo to a constant value of 300 revolutions per minute (RPM).

The track movement mechanism which moves the magnetic head is driven by a stepping motor. The stepping motor moves the magnetic head by one track of distance per stepping pulse. It takes 6 ms.

Data can be recorded to floppy disks by using the modified frequency modulation (MFM) system, so that the floppy

- 42 -

disk controller can decode data to be recorded and encode the data read out. The effective track width, after recording, is 0.115 mm and the track pitch is 0.1875 mm, so that the track density is 135 tracks per inch (tpi). The magnetic head can seek desired data irrespective of whether the spindle motor is rotating or not, so that the system can activate the spindle motor and also seek desired data at the same time.

Each floppy disk drive has the following built-in sensors, whose output is sent to and used by the floppy disk controller, which in turn controls the operation of the drive.

- Sensor which detects whether the head is positioned to track 00 (the outermost track)

- Sensor which detects the start point of a track (This sensor actually detects the index hole.)

- Sensor which detects whether the write inhibit hole is made (write-protected) or not

- · Sensor whether a floppy disk is taken out of the drive

- 43 -

2.9 Floppy Disk Controller (FDC)

The MultiSpeed employs as the floppy disk controller (FDC) the µPD-72065G programmable floppy disk controller. This controller is positioned between the system bus and the floppy disk drive (FDD) to control the FDD operation and relay the data transferred between the FDD and the system data bus.

Data (8-bit parallel data) are transferred from memory via the data bus to the FDC, which in turn converts those data to serial data and then sends them to the FDD with both a timing clock and a cyclic redundancy code (CRC) attached to them. At the FDC the serial data read out from the FDD undergo such processes as CRC checking, separation of clock and data, and conversion into parallel data, which are then transferred to memory via the system data bus.

The direct memory access (DMA) method is employed in data transfer between memory and the FDC. The FDC, moreover, causes a hardware interrupt of level 6 either when a read/ write operation to a floppy disk is terminated or when a request must be made to the processor to read the status of the FDC itself.

The FDC supports the recording system of such sepcifications as double-sided, double-density, and modified frequency modulation (MFM), providing the floppy disk format compatibilities with the IBM.

- 44 -

The FDC is provided with a standby function to reduce power consumption. With the standby function, the FDC is automatically powered off when it is not accessed by the system. In the standby mode, therefore, disk accessing takes a long time as compared with that in the general mode. The FDC can be set in the standby mode by MultiSpeed application "Setup" as well as by the BIOS routine.

By connecting the external floppy disk controller (EXT. FDC) connector on the MultiSpeed body rear pannel to the IBM personal computer at its expansion drive connector, the 3.5-inch MultiSpeed FDD can be used as an expansion drive of that IBM machine. In this case, the FDC of Multi-Speed itself is disconnected from the system.

#### \* Programming considerations

The FDC uses the following registers, listed below, to provide control by software or read out the FDC status or data.

| (hex) | R/W | Usage                |

|-------|-----|----------------------|

| 3F2   | Ŵ   | FDC Control Register |

| 3F4   | R   | FDC Status Register  |

| 3F5   | R/W | FDC Data Register    |

#### FDC Control Register: 3F2 (hex)

The FDC control register (DOR) is used, for example, to select drives, turn the drive spindle motor ON/OFF, reset

- 45 -

the FDC, or enable DMA or interrupts.

Bit Usage

- 7 6 Not used

- 5 Drive B motor on

- 4 Drive A Motor on

3 Enable FDC Interrupt/DMA

This bit enables both FDC interrupt requests and DMA transfer requests. If this bit is reset, neither the FDC interrupt request nor the DMA transfer request is enabled.

2 FDC Reset

This bit, when set to 0, resets the FDC and fixes it in idle status. This bit is set by the program which enables the FDC.

1 - 0 Drive Select

These bits are decoded to select the desired drive. These bits, however, are ignored if the drive thus selected has already been set off by bit 4 or 5.

Bit 10 Drive 00 Drive A 01 Drive B 10 Not used 11 Not used

#### FDC Status Register: 3F4 (hex)

Bit Usage

7 Request for master.

Indicates whether the FDC data register is ready for read/write operation. When this bit is 1, the data register is ready.

6 Data Input/Output

Indicates the direction in which data are transferred between the processor and the FDC data register, as follows:

- 0: Data are transferred from the processor to the data register.

- Data are transferred from the data register to the processor.

5 Non-DMA mode

When this bit is 1, the FDC operates in non-DMA mode. (The DMA system is not used in data transfer.)

4 FDC Busy

Indicates that the FDC is in read, write, or seek operation.

- 3 2 Reserved

- 1 FDD-B Busy

Indicates that drive B is in the seek mode.

0 FDD-A Busy

Indicates that drive A is in the seek mode.

- 47 -

## FDC Data Register: 3F5 (hex)

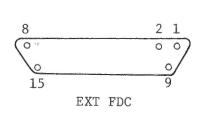

This 8-bit register actually comprises multiple subregisters, each of which can be read out for each access. These sub-registers store the data, command, parameter, and FDD status information. Data bytes read out of or written to this register are used to obtain the results of executing programs or special commands. 2.10 External Floppy Disk Controller (EXT FDC) Interface

This interface, a 15-pin connector, is used to connect the FDD built in the MultiSpeed to the IBM personal computer's floppy disk controller. To actually connect them, the "IBM cable kit" is employed. What follows will explain the pins of this connector. In the following explanation, the plus (+) or minus (-) sign immediately preceding the signal name indicates the active state of the relevant signal. Also, I (input) or O (output) given in the I/O column in the table below indicates the signal feeding direction as viewed from the connector.

- 49 -

| Pin No. | Signal name         | 1/0 | Explanation                                                                                                                                                                                                                                                                                                      |

|---------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | - Index             | 0   | This negative-logic pulse<br>signal indicates the start<br>point for tracks; as many a one<br>is given for each revolution of<br>the disk.                                                                                                                                                                       |

| 2       | - Motor 3<br>Enable | I   | This signal, when set to the<br>low level, turns on the motor<br>for MultiSpeed drive A.                                                                                                                                                                                                                         |

| 3       | - Drive 4<br>Select | I   | This signal selects MultiSpeed<br>drive B.                                                                                                                                                                                                                                                                       |

| 4       | - Drive 3<br>Select | I   | This signal selects MultiSpeed<br>drive A.                                                                                                                                                                                                                                                                       |

| 5       | - Motor 4<br>Enable | I   | This signal, when set to the<br>low level, turns the motor on<br>for MultiSpeed drive B.                                                                                                                                                                                                                         |

| 6       | - Direction         | I   | This signal specifies the direc-<br>tion in which to move the read/<br>write head, when the step<br>signal is received. This<br>signal moves the head to the<br>center of the disk when it is<br>set to low level. When it is<br>sent to high level, it moves the<br>head to the outermost track of<br>the disk. |

| 7       | - Step              | I   | This signal moves the read/<br>write head by as much as one<br>track per pulse.                                                                                                                                                                                                                                  |

- 50 -

| Pin No. | Signal name        | I/0 | Explanation                                                                                                                       |

|---------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| 8       | - Write<br>Data    | I   | This signal, when the Write<br>Enable signal is active, is<br>recorded as a change in<br>magnetism, onto disks.                   |

| 9       | - Write<br>Enable  | I   | This signal, when set to low<br>level, enables data to be<br>written to disks.                                                    |

| 10      | - Track O          | 0   | This signal, when set to low<br>level, indicates that the head<br>for a selected drive is posi-<br>tioned at the outermost track. |

| 11      | - Write<br>Protect | 0   | This signal, when set to low<br>level, indicates that a selected<br>drive is write-protected.                                     |

| 12      | - Read Data        | 0   | This is the regenerative pulse<br>signal which indicates the<br>information recorded on disks.                                    |

| 13      | - Head<br>Select   | I   | This signal, when set to low<br>level, selects the upper head<br>of a selected drive.                                             |

| 14      | GND                |     |                                                                                                                                   |

| 15      | GND                |     |                                                                                                                                   |

#### 2.11 Real-Time Clock

As the real-time clock the MultiSpeed employs the RTC-58321. The real-time clock has its own built-in crystal oscillator, to support the timer function and the 100-year calendar.

The timer function enables the user to select the 12-hour mode or the 24-hour mode, supplying the count data for time (hour, minute, and second). The calendar, on the other hand, supports a function to automatically adjust month-end dates and leap years.

#### \* Programming considerations

One or two counters are provided to correspond to each of the year, month, day, day-of-the-week, hour, minute, and second data. Each of those counters is assigned a 4-bit internal address, to count 4-bit data. The count data can be read or written by writing the corresponding internal address content to I/O address OE4(hex) and subsequently specifying read or write operation respectively; one counter of data is read or written each time this operation is executed. However, the internal address cords, hex D, hex E and hex F, are not used to specify any internal counter. Those internal address cords are interpreted as the command for the real-time clock.

- 52 -

Fig. 2.11.1 gives the correspondence between the internal counter and the internal address.

Fig. 2.11.1 Internal counters and internal address

| Internal         | Internal | Count   |                   |        |  |  |

|------------------|----------|---------|-------------------|--------|--|--|

| address<br>(hex) | counter  | value   | Usage             |        |  |  |

| 0                | Sl       | 0 — 9   | Low-order digit   | Second |  |  |

| 1                | S2       | 0 - 5   | High-order digit  | Second |  |  |

| 2                | Mll      | 0 - 9   | Low-order digit   | Minute |  |  |

| 3                | Ml2      | 0 - 5   | High-order digit  | MINUTE |  |  |

| 4                | н1       | 0 9     | Low-order digit   | Hour   |  |  |

| 5                | Н2       | 0-1/0-2 | High-order digit  | nour   |  |  |

| 6                | W        | 0 - 6   | Day-of-the-wee    | k      |  |  |

| 7                | Dl       | 0 9     | Low-order digit   | Day    |  |  |

| . 8              | D2       | 0 - 3   | High-order digit  | Day    |  |  |

| 9                | MOl      | 0 9     | Low-order digit   | Month  |  |  |

| A                | M0 2     | 0 - 1   | High-order digit  | MOILUI |  |  |

| В                | Yl       | 0 - 9   | Low-order digit   | Year   |  |  |

| C                | ¥2       | 0 - 9   | High-order digit  | IEal   |  |  |

| D                | -        |         | Counter resetting |        |  |  |

| E - F            |          |         | Reference signal  | output |  |  |

Real-Time Clock Control Register (Calendar Chip): 0E4(hex)

This register is used to read the time or date data from or write it to the real-time clock, specifically storing the counter's internal address, read/write direction, etc.

When the register is written;

|     | 7 6 5 4 3 2 1 0                              |

|-----|----------------------------------------------|

|     | CS DIR AWS RD WR D3 D2 D1 D0                 |

|     |                                              |

| Bit | Usage                                        |

| 7   | Chip Select bit. This bit is set to 1 in all |

|     | cases in which data is written.              |

| 6   | Direction bit                                |

Data/internal address contents are written 1: in.

Data is read out. 0:

5 Address Write Strobe bit. When this bit is set to 1, the content of the four low-order bits of this register is latched as the internal address.

Read/Write Strobe bit. When this bit is set 4 to 1, the system executes read/write operation to the counter of an internal address which has been latched, with the low-order four bits of this register assumed to be the count data.

- 54 -

3 - 0 These four bits store the internal address of

count data to be written in. The LSB is bit 0. When the register is read:

| 7    | 6 | 5 | 4 | 3               | 2  | 1  | 0  |

|------|---|---|---|-----------------|----|----|----|

| BUSY |   |   |   | <sup>-</sup> D3 | D2 | D1 | DO |

Bit Usage

7 Real-time clock busy bit

6 - 4 Not used

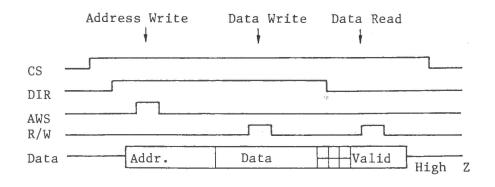

Fig. 2.11.2 below shows a timing chart for internal counter read/write operation by combination of the high-order four bits.

# Fig. 2.11.2 Timing chart for count data read/write operation

H2 Counter: Internal address 5(hex) This counter counts the high-order digit ("l0s" digit) of the hour data.

Bit Usage

3 This bit selects the 24-hour/12-hour mode. If this bit is set to 1, bit 2 is automatically reset to 0.

0: 12-hour mode

1: 24-hour mode

2 0 = AM

1 = PM

1 - 0 These two bits are used to count the highorder digit of the hour data.

D2 Counter: Internal address 8(hex) This counter counts the high-order digit ("los" digit) of the date.

Bit Usage